≪2006年度≫

■研究の概要

- 画像処理、暗号処理、符号化処理等の領域を統合する方式をメディア情報の重要度に応じて、暗号強度や誤り訂正能力を適応的に変化させ、統合的観点から消費電力を削減する基本方式を検討した。動画圧縮処理と誤り訂正処理を最適に組合せると従来の処理を独立に行う方法に比べて、動画の品質を保ちながら、40%の計算量を減らす方式を考案した。

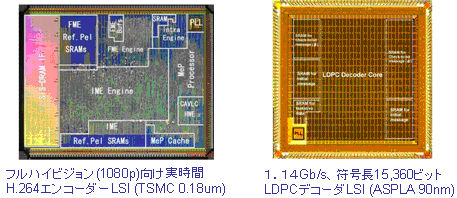

- 動画像処理に対してH.264エンコーダチップの低消費電力化を図り、現状までに提案されている最良方式に比べて、約1/2の電力で実行できることを確認した。

- ハードウェア指向設計の研究において、アルゴリズムレベルで最適化されたC/C++ のプログラムに対し、それをハードウェアとして実現する上での低消費電力を目指した高位レベルでの配置配線の評価精度を向上する新しいモデリングを用いたフロアプラン手法の基本アルゴリズムの研究を行った。

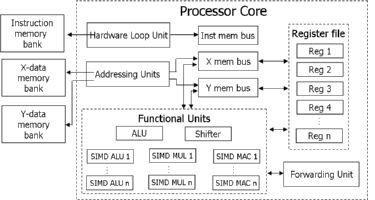

- ソフトウェア指向設計の研究では、新たな低電力化プロセッサを開発しその上に搭載されるソフトウェア面に着目して超低消費電力化を目指し、コンフィギュラブルプロセッサの概念を導入し、「不必要な命令」の削除、とりわけメモリアクセス最小化の観点から、アプリケーションプログラムに対して最適な命令再合成アルゴリズムの構築に取り組んだ。

■成果発表

・原著論文発表(国際6件)

- Yang Song, Zhenyu Liu, Takeshi Ikenaga, Satoshi Goto, "Low-Power Partial Distortion Sorting Fast Motion Estimation Algorithms and VLSI Implementation", IEICE Trans. Inf. & Syst., Vol. E90-D, No. 1, pp. 108-117, Jan. 2007.

- Shen Li, Lingfeng Li, Takeshi Ikenaga, Shunichi Ishiwata, Masataka Matsui, Satoshi Goto, "Content-based complexity reduction methods for MPEG-2 to H.264 video transcoding", IEICE Trans. Inf. & Syst., Vol. E90-D, No. 1, pp. 90-98, Jan. 2007.

- Zhenyu Liu, Yang Song, Satoshi Goto, Takeshi Ikenaga, "A Fine-Grain Scalable and Low Memory Cost Variable Block Size Motion Estimation Architecture for H.264/AVC", IEICE Trans. Electronics, Vol. E89-C, No. 12, pp. 1928-1936, Dec. 2006.

- Kazunori Shimizu, Tatsuyuki Ishikawa, Nozomu Togawa, Takeshi Ikenaga, Satoshi Goto, "Power-Efficient LDPC Decoder Architecture based on Accelerated Message-Passing Schedule", IEICE Trans. Fundamentals, Vol. E89-A, No. 12, pp. 3602-3612, Dec. 2006.

- Yang Song, Zhenyu Liu, Takeshi Ikenaga, Satoshi Goto, "A VLSI Architecture for Variable Block Size Motion Estimation in H.264/AVC with Low Cost Memory Organization", IEICE Trans. Fundamentals, Vol. E89-A, No. 12, pp. 3594-3601, Dec. 2006

- Nobuhiro DOI, Takashi HORIYAMA, Masaki NAKANISHI, and Shinji KIMURA, "Bit-Length Optimization Method for High-Level Synthesis based on Non-Linear Programming Technique," IEICE Trans. on Fundamentals, Vol. E89-A, No. 12, pp.3427-3434, Dec. 2006.

・国際学会および主要な国内学会発表(国内16件、国際11件)

- 李 星、清水一範、池永 剛、後藤 敏、"高効率Message-Passing スケジュールを用いた部分並列型イレギュラーLDPC復号器", 電子情報通信学会集積回路研究会, Mar. 2007.

- 神園: 線形計画法を用いたクロックスキューの最適化, 情処学会九州支部「火の国シンポジウム2007」講演No. C-2-1(2007年3月)

- Shen Li, Xianghui Wei, Takeshi Ikenaga, Satoshi Goto, "A VLSI Architecture Design of an Edge Based Fast Intra Prediction Mode Decision Algorithm for H.264/AVC", ACM Great Lakes Symposium on VLSI (GLSVLSI 2007), Mar. 2007.

- Zhenyu Liu, Yiqing Huang, Yang Song, Satoshi Goto, Takeshi Ikenaga, "Hardware-Efficient Propagate Partial SAD Architecture for Variable Block Size Motion Estimation in H.264/AVC", ACM Great Lakes Symposium on VLSI (GLSVLSI 2007), Mar. 2007.

■受賞

- 吉村:IEEE APCCAS 2006 Best Paper Award, 2006年12月("On the number of 3-D IC floorplan configurations and A Solution Perturbation Method with Good Convergence")

≪2007年度≫

■研究の概要

メデイア情報処理システムの超低消費電力化実現のために、画像、暗号、誤り訂正符号の各方式の最適な分担、およびアルゴリズムの最適化をはかり、ハードウェア実装とソフトウェア実装の各観点から最適化をはかり、超低消費電力LSIチップを開発し、従来技術と比較して1/100の電力削減を図ることで研究を進めている。

- 本年度は画像と暗号の一体化、画像と誤り訂正の一体化をデータ重要度に応じて処理の深さを変え、人間にとっては遜色のない、かつ安全性も保たれる技術を開発した。その結果、個々の技術で1/2程度の計算量を削減し、トータルで1/4程度の計算量を削減できた。

- 最も計算量と消費電力が必要となる画像のエンコーダに対して1/2〜1/3の消費電力で実行可能なLSIを開発した。

- 3次元フロアープランの導入で25%のダイナミックパワーの削減を図れることが分かった。

- 新しいパワーゲーテイング手法の導入で、28%の電力削減を行うことができた。

- オペコードビット/オペランド削減アルゴリズム、エネルギー最小化アルゴリズムの3つのアルゴリズムによって、プロセッサ全体で最大12%の消費エネルギーを削減することができた。

■成果発表

・原著論文発表(国内2件、国際13件)

- 森隆寛, 外村 元伸, 大住 勇治, 後藤 敏, 池永 剛, "キュービック補間に基づく魚眼画像の高画質補正アルゴリズム及び専用ハードウェアエンジンの提案", 画像電子学会誌, Vol. 36, No. 9, pp.680-687, Sep., 2007

- 伊東 健, 中村 創, 後藤 敏, 池永 剛, "デジタルシネマ用JPEG 2000 エンコーダ向け並列CBMアルゴリズム及びLSI アーキテクチャ", 画像電子学会誌, Vol. 36, No. 9, pp.650-656, Sep., 2007

- Xiang-hui Wei, Shen Li, Yang Song, Satoshi Goto, "An Irregular Search Window Reuse Scheme for MPEG-2 to H.264 Transcoding", IEICE Special Section on Signal Processing for Audio and Visual Systems and Its Implementaion, pp.749-755, Mar., 2008

- Yibo Fan, Jidong Wang, Takeshi Ikenaga, Yukiyasu Tsunoo, Satoshi Goto, "An Unequal Secure Encryption Scheme For H.264/AVC Video Compression Standard", IEICE Trans. Fundamentals, Vol. E91-A, No.1, pp. 12-21 Jan. 2008

・国際学会および主要な国内学会発表

<招待講演:国内5件、国際4件>

- 後藤 敏、“情報・電気・電子グローバルCOEの戦略と計画”、電子情報通信学会総合大会、TK-6-13、2008年3月

- 後藤 敏、“シリコンシーベルト福岡”、電子情報通信学会総合大会、ACK-1-2,2008年3月

- Satoshi Goto, ”Paradigm shift for System LSI design methodology”,2007 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS 2007), Xiamen, China, Nov. 2?7 (Keynote Speech)

- Takeshi Yoshimura and Song Chen, “A Fixed-Outline Floorplanning Method”, Proceedings of ASICON2007, Oct. 2007

<口頭講演:国内47件、国際38件>

- WANG Lu, ZHANG Xiaolin, CHEN Song, and YOSHIMURA Takeshi, “On Objective Functions for Fixed-Outline Floorplanning”, 電子情報通信学会2008年総合大会

- XU Zheng, CHEN Song, and YOSHIMURA Takeshi, “A Multilevel Fixed-outline Floorplanning for Large-scale IC Design”, 電子情報通信学会2008年総合大会

- Yuta Abe, Xing Li, Kazunori Shimizu, Takeshi Ikenaga, Satoshi Goto, "High-throughput design of high-efficiency message passing partially parallel irregular-LDPC decoder based on 802.11n", International Conference in Embedded Systems and Intelligent Technology (ICESIT 2008), Feb., 2008

- Youhua Shi, Nozomu Togawa, Masao Yanagisawa, Tatsuo Ohtsuki, "GECOM: Test Data Compression Combined with All Unknown Response Masking, ASP-DAC 2008", pp.577-582, COEX, Seoul, Korea, Jan. 24, 2008

■受賞

- Samsung Electronics Award Silver Prize, Oct. 2007. Yao Ma, Yang Song, Takeshi Ikenaga, Satoshi Goto, "A High Throughput Multiple Transform Architecture for H.264/AVC Fidelity Range Extensions", International SoC Design Conference (ISOCC 2007)

- 第9回LSI IPデザイン・アワード IP賞: 清水一範、池永剛、後藤敏、"1.14Gb/s 15360bit LDPC符号復号器", Apr. 2007.

- 情報処理学会システムLSI設計技術研究会・ 2006年度優秀発表学生賞:小原俊逸、大智輝、奈良竜太

- 情報処理学会コンピュータサイエンス領域奨励賞:大智輝

- 情報処理学会システムLSI設計技術研究会優秀論文賞:大智輝

■新聞報道

- 6月19日 日刊工業新聞: フルハイビジョンH.264エンコーダLSIを開発

|